This post is a part of the series on audio amplifier feedback. The contents of the series can be found here.

In the previous post, I explained how current dumping works on an intuitive, qualitative level. Let's go into the next level of detail.

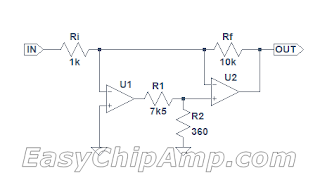

A current dumping amplifier is a feedback amplifier consisting of a low distortion, low power amplifier A and a high-power, distorting buffer ("current dumper", here Tr1 and Tr2) inside a common negative feedback loop:

Negative feedback reduces, but not completely eliminates, the distortion that the current dumper adds to the signal. From my earlier post, the share of that distortion that remains at the output (point D at the schematic above) after the negative feedback is applied is given by the Error Transfer Function $${ETF={1 \over {1- A \times B}}}$$ where $A$ is the transfer function (basically, the frequency-dependent gain) of the integrator composed of A,R1,C1, and $B$ is the transfer function of the feedback network. In this case, the feedback network has unity gain and is connected to the inverting input of the integrator, so $B=-1$, and $${ETF={1 \over {1+ A}}}$$ Therefore of the total open loop distortion $\epsilon$ of the current dumper, at point D we observe $$\epsilon _D={\epsilon \times ETF}=\epsilon {1 \over {1+ A}}$$ Since the current dumper adds distortion $\epsilon$, for this to happen, the input of the current dumper (point A at the schematic above) should see "pre-distortion" $$ \epsilon _A = {\epsilon_D - \epsilon}={{\epsilon {1\over {1+ A}}}-\epsilon}=-\epsilon{A \over {1+ A}}$$ At the load, $\epsilon_A$ and $\epsilon_D$ combine in reverse proportion to the impedances of R2 and L1: $$\epsilon_{LOAD}\propto {\epsilon_A Z_{L_1} + \epsilon_D Z_{R_2}}$$ Note that the load impedance affects the absolute level of the combined signal at the load but not the proportion of $\epsilon_A$ to $\epsilon_D$.

Combining the last three equations and dropping the common denominator $1+A$: $$\epsilon_{LOAD}\propto {\epsilon (Z_{R_2} - A Z_{L_1})}$$

Clearly, the perfect cancellation of the current dumper's distortion occurs when $$Z_{R_2} = A Z_{L_1}$$

For the implementation above, under ideal conditions, $Z_{R_2}= {R_2}$, $Z_{L_1}= s {L_1}$, $A=1/{(s R_1 C_1)}$, and the perfect cancellation means

$$R_2={L_1 \over {R_1 C_1}}$$

which is the result from [1]: "For the linearity of Tr1 and Tr2 to be immaterial then L must equal RRC".

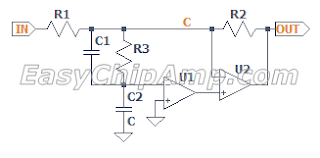

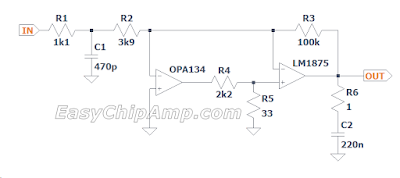

However, by going through the algebra above, we obtained a more general and quite remarkable result: a perfect distortion cancellation requires the ratio of $Z_{R_2} / Z_{L_1}$ to mimic the amplifier's loop gain $A$. This gives us the freedom to make current dumping work under less than ideal conditions, as well as in different implementations than Walker's.

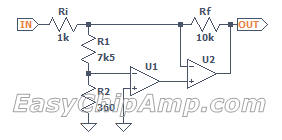

For example, the gain of an ideal integrator $A=1/{(s R_1 C_1)}$ is infinite at DC, which is practically impossible. A more realistic integrator has a transfer function $A=A_0/{(1+s{T_p})}$, where $A_0$ is the finite DC gain and $T_p$ is the time constant corresponding to the integrator's single pole. Substituting this into our perfect cancellation condition $Z_{R_2} = A Z_{L_1}$, we obtain $${Z_{L_1}} = {R_2 \over A} = {R_2 \over A_0}{ (1+s{T_p})} = {R_2 \over A_0}+s {R_2 T_p \over A_0}$$

Since the impedance of a realistic inductor is $$Z_L=R_{ser}+sL$$where $Rser$ is the DC resistance and $L$ is the inductance, it is clear that ${R_2 T_p / A_0}$ corresponds to the inductance, and ${R_2/A_0}$, to the DC resistance of the inductor providing a perfect distortion cancellation.

Since we have five variables $L_1$, $R_{ser}$, $R_2$, $A_0$, $T_p$ and two equations $L_1={R_2 T_p / A_0}$ and $R_{ser}={R_2/A_0}$, any three variables can be chosen freely. Note that $A_0$ and $T_p$ together determine the unity-loop-gain frequency $F_0=A_0/(2 \pi T_p)$, which may be a more meaningful parameter.

Finally, let's make a quick reality check and see if the ideal distortion cancellation in this example can still be implemented with reasonable parts. In my previous post, I found that a perfect cancellation is possible with a L=3.3μH inductor, R2=21ohm resistor and an amplifier with the unity-loop-gain frequency F0 of 1 MHz. With the DC gain of the amplifier at, say, 80dB (×10k), the DC resistance of the inductor should be 21/10k=2.1mOhm for a perfect low-frequency cancellation. This looks too low to be implemented in real hardware, esp. after the impedance of PCB traces, etc., is taken into account. One way to address this is to reduce the DC gain (and hence the loop gain at the frequencies below the amplifier's pole) while keeping the same unity-loop-gain frequency. Another would be to increase the unity-loop-gain frequency, which would require a proportional increase in R2 and Rser. However, practically speaking, the perfect cancellation at low frequencies may not be as important, as the amplifier has more loop gain there, and the feedback, rather than feedforward, will take care of the distortion of the output stage.

Stay tuned for an implementation of current dumping different from Walker's.

References

- P. J. Walker and M. P. Albinson, "Current Dumping Audio Amplifier," presented at the 50th AES convention, March 1975.

- S. Takahashi and S. Tanaka, “Design and Construction of a Feedforward Error Correction Amplifier,” JAES vol. 29, pp. 31-37, Jan/Feb 1981.